-

图文详情

-

产品属性

-

相关推荐

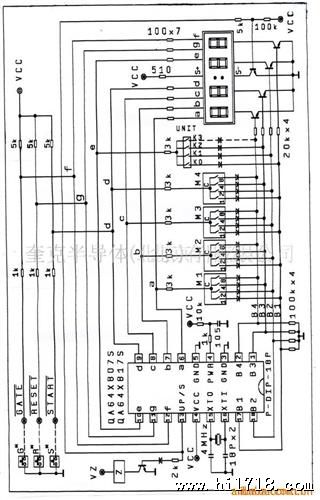

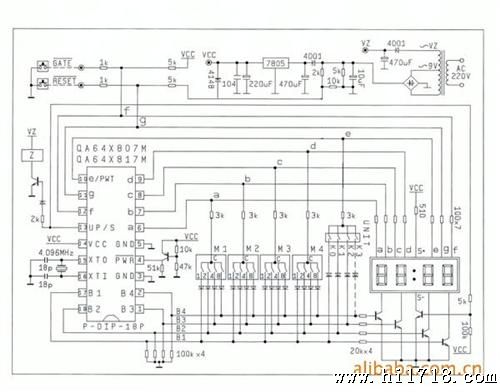

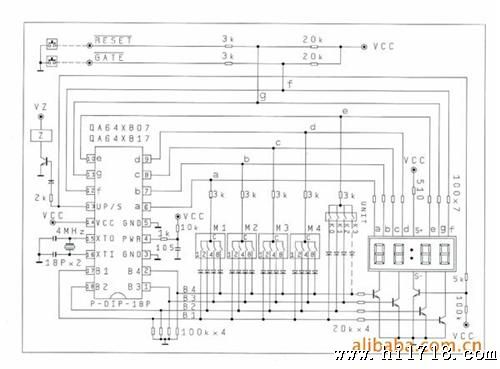

高、高抗扰,码盘整定4位数显时间继电器系列电路

(查看详细产品说明书,敬请点击商铺左侧“友情链接”【奎克半导体简体中文网站 】进入奎克公司网站,在浏览器地址栏公司网址后续接“/QA807.htm”进行查阅)

《QA64X807系列选型指南》

(型号中“X”不同,表示电路的时间单位选择表不同。详见《时间单位及计时范围》)

快速重复上电复位型 | |||

| 正计时 | 倒计时 | 功能区别 | 价格 |

| QA64X807L | QA64X817L | 具复位控制 | N档 |

| QA64X807M | QA64X817M | 具复位、暂停控制 | N档 |

| QA64X807N | QA64X817N | 具复位、暂停、启动控制 | N档 |

| QA64X807NG | QA64X817NG | 具复位、暂停(下沿有效)、启动控制 | N档 |

.

具小数点显示控制、快速重复上电复位型 | |||

| 正计时 | 倒计时 | 功能区别 | 价格 |

| QA64X807DL | QA64X817DL | 具复位控制 | E档 |

| QA64X807DM | QA64X817DM | 具复位、暂停控制 | E档 |

| QA64X807DN | QA64X817DN | 具复位、暂停、启动控制 | E档 |

| QA64X807DNG | QA64X817DNG | 具复位、暂停(下沿有效)、启动控制 | E档 |

.

具小数点显示控制、单片式掉电免备电数据保持型 | |||

| 正计时 | 倒计时 | 功能区别 | 价格 |

| QA64X807DL-F | QA64X817DL-F | 具复位控制 | T档 |

| QA64X807DM-F | QA64X817DM-F | 具复位、暂停控制 | T档 |

| QA64X807DN-F | QA64X817DN-F | 具复位、暂停、启动控制 | T档 |

| QA64X807DNG-F | QA64X817DNG-F | 具复位、暂停(下沿有效)、启动控制 | T档 |

.

.

普通上电复位型 | |||

| 正计时 | 倒计时 | 功能区别 | 价格 |

| QA64X807 | QA64X817 | 具复位、暂停控制 | E档 |

| QA64X807S | QA64X817S | 具复位、暂停、启动控制 | E档 |

| QA64X807SR | QA64X17SR | 具复位、启动控制 | E档 |

.

掉电备用电源数据保持型 | |||

| 正计时 | 倒计时 | 功能区别 | 价格 |

| QA64X807-W | QA64X817-W | 具复位、暂停控制 | E档 |

| QA64X807S-W | QA64X817S-W | 具复位、暂停、启动控制 | E档 |

.

LSI CMOS

.

18脚双列直插或SOIC贴片封装。

型号中“X”不同,表示电路的时间单位选择表不同,其UNIT选择开关(K3)、K2、K1、K0选择的不同时基表见《时间单位及计时范围》。表中(K3)、K2、K1、K0开关“ON”为“1”,“OFF”为“0”。当选择实时钟方式(“XX分:XX秒”或“XX小时:XX分”)时,高两位未达整定值前,低两位为60进制,高两位达到整定值后,低两位可按整定值从1计到99。

具小数点自动显示控制的电路,小数点随所选时间单位自动改变位置,并兼做秒闪烁。全整数时小数点显示在个位右侧,仅做为秒闪烁显示。

四位数字显示。直接驱动共阴LED,无需外接译码器。型号后加尾字母A、B、C可选三种无效零消隐类型(A可不加):A型,高位无效零消隐;B型,实时钟方式时百位不消隐;C型,高位无效零不消隐。

暂停功能由门控开关GATE实现。QA64X807NG、QA64X817NG、QA64X807DNG、QA64X817DNG、QA64X807DNG-F、QA64X817DNG-F门控开关GATE下沿有效,暂停/计时反复控制。其它电路门控开关GATE电平有效,低电平暂停,高电平计时。

启动功能由启动开关START实现,开关“ON”启动计时。

具片内上电复位电路和外控复位电路。外控复位开关RESET“接地”(低电平)为复位,复位中显示“0”。RESET及START开关低电平宽度必须大于100mS才为有效,从而增强抗扰和防抖能力。

不用外控复位、启动或门控时,相应开关及接开关的电阻可省,但接电源的电阻应保留。

具“定时符合与秒信号闪烁”复用输出端(UP/S):计时过程中可按秒信号闪烁,每0.5秒交替呈现“高阻”(亮)或 “0”(灭)。见应用举例。启动后先亮后灭,符合后停在亮。门控暂停时灭。

由M1(个)、M2(十)、M3(百)、M4(千)四个8,4,2,1码拨盘整定预定值。码盘缺省整定值为零。

.

《快速重复上电型电路》

详见图4~图6、图9~图10。由“片内上电复位电路外接调整端”PWR与“早期电源测试”端PWT(复用端)配合,可很好的解决即要提高电路抗电源干扰的能力,又要电路在电源跌落时能够快速复位以缩短重复上电间隔时间这样一对矛盾,而不必总靠减小VCC处的电源时间常数。例如,按应用举例电路连接,凡不低于2V、不宽于50毫秒的电源跌落电路不会被干扰复位。 PWT所接处电源时间常数应小于VCC处电源时间常数,至少应使PWT处电源跌至2V的时间比VCC处跌至2V的时间早50毫秒以上。

.

《备电低功耗数据保持型电路》

应用举例见图7、图8。当主电V+掉电后,芯片仅需由备电VB提供多5μA的保持电流(典型值0.1μA)。VB与V+无严格要求,只要使VCC端电压符合VCC电源范围要求即可。在低功耗保持期间,芯片能记忆当时已进行的数据状态。为降低芯片功耗,除电源测试端PUB仍为输入端外,其它全部入出端口均变为输出口且输出“0”电平。当V+恢复供电时,在PUB端产生一个负脉冲,使芯片从掉电时刻状态起继续工作。因从V+恢复供电到芯片各输入端恢复为输入态约需2mS时间,为避免瞬时短路,需接高电平的输入端应通过小0.5K的上拉电阻接V+,避免直接接电源。

.

《免备电数据保持型电路》

应用实例见图12~图14。当电源掉电后,芯片能长期(大于40年)记忆掉电时已进行的数据状态,电源恢复供电后,芯片从掉电时刻状态起继续工作。PWT所接处电源时间常数应至少小于VCC处电源时间常数50毫秒以上。