-

图文详情

-

产品属性

-

相关推荐

设计依据:

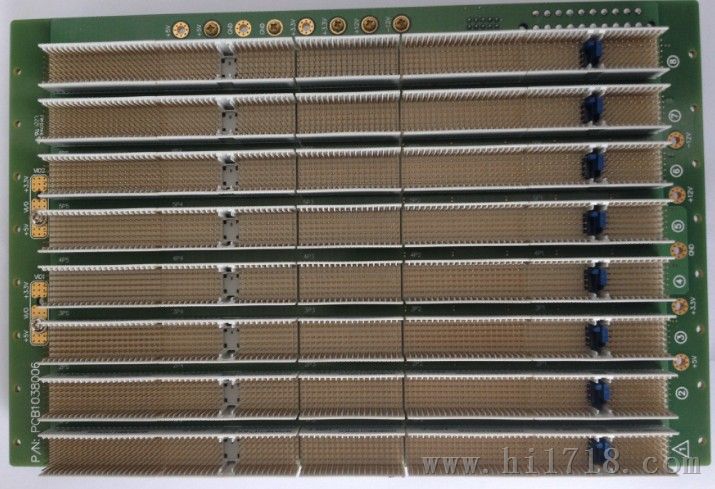

CPCI Specification PICMG 2.0 R3.0 (October 1, 1999)

CPCI Hot Swap Specification PICMG 2.1 R1.0 (August 3, 1998)

CPCI System Management Specification PICMG 2.9 R1.0 (February 2, 2000)

Keying of CPCI Boards and Backplanes PICMG 2.10 R1.0 (October 1, 1999)

CPCI Power Interface Specification PICMG 2.11 R1.0 (October1, 1999)

总线结构:

P5 | Rear IO | |||||||

P4 | ||||||||

P3 | ||||||||

P2 | 64bit\33MHz CPCI Bus | |||||||

P1 | ||||||||

Slot | 1 | 2 | 3 | 4 | 5 | 6 | 7 | 8 |

| 系统 | 外围槽 | ||||||

技术参数:

槽数 : 1 System Slot + 7 Peripheral slots ;

结构尺寸 : 26 2.05 x 1 61.72 x 3.8 mm(H×W×T);

电源输入方式:M3接线柱方式,ATX供电方式;

背板电压降 : <20mV ;

V(I/O): +3.3V / +5V 可选,出厂默认+5V;

单端阻抗 : 65ohm ±10% for trace.

工作温度 : 0 ℃ ~ + 55 ℃

贮存温度 : -40 ℃ ~ +85 ℃

MTBF: 700,000h