汽车电子自适应频率调制DC/DC降压变换器的设计

发布时间:2019/1/22 8:47:00目前,高频、高效的DC/DC转换器在汽车电子系统中的应用越来越多。高开关频率可以使用较小的功率电感和输出滤波电容,从而减小系统的体积,提高紧凑性并降低成本。高工作效率可以延长汽车电池的使用时间,降低系统功耗,从而减少发热量,优化系统的热设计并进一步提高可靠性。但高开关频率会降低系统的工作效率。因此设计汽车电子应用的DC/DC降压变换器时必须在开关频率和工作效率之间作一些折衷处理。

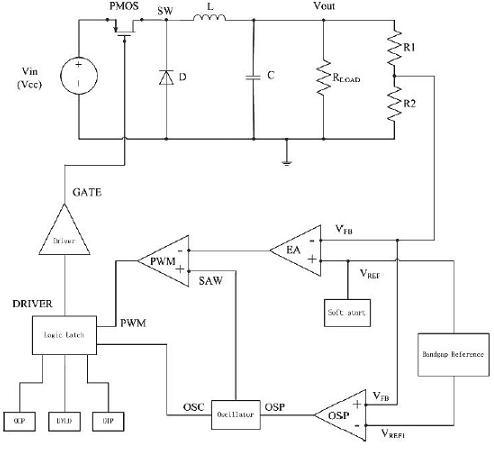

DC/DC降压变换器的开关频率受限于DC/DC的输入电压、输出电压和功率管的开启时间,理论极限值可以由下式计算:

公式1

其中fSW(MAX)为的开关频率,tON(MIN)为开关管要求的导通时间,VD是续流二极管的正向压降,VOUT为正常工作的输入电压,VSW为开关管的导通压降。上式表明tON(MIN)一定时,低占空比要求更低的开关频率才能保证系统安全的操作,同样低开关频率容许更低的输出输入电压比值。输入电压依赖于开关频率的主要原因在于PWM控制器具有的导通时间tON(MIN)和截止时间tOFF(MIN)。如果取值为100ns,即开关管开通时的导通时间至少要持续100ns,低于100ns可能导致功率管MOSFET无法正常开启。同样开关管关断时的截止时间至少要持续100ns,低于100ns可能导致MOSFET无法正常关断。这意味着和占空比为:

公式2

这里fSW是开关频率,tON(MIN)是的导通时间和tOFF(MIN)是的截止时间。

上式表明开关频率降低时,占空比的范围增加。输入输出的电压范围也可以增加。优化的开关频率可以保证系统在电感和电容值尽可能小的情况下能够具有足够宽的输入工作电压范围。

通常DC/DC电源芯片的输入电压有额定的工作电压范围。除了额定工作电压的限制,实际的输入电压还受到其他一些条件的限制,的实际输入工作电压通常由的占空比决定。在输入电压时,占空比,所以在输出电压一定的条件下的实际输入工作电压由PWM控制器的占空比决定。tON(MIN)是每个控制器能够接通高端MOSFET的最短持续时间。它由内部定时延时以及接通高端MOSFET所需要的栅极电荷量决定,低占空比的应用可以接近该最短导通时间限制。

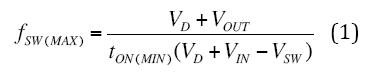

通常DC/DC电源芯片的开关频率是固定的,但是如果我们可以在输入电压增加时降低开关频率,就可以扩大占空比的范围,从而在保证输出电压的条件下扩大输入电压的范围。在很多DC/DC电源芯片中,通过一个管脚对地接一个电阻来设定DC/DC的开关工作频率。一个典型的应用电路如图1所示。

图1: 一种典型的DC/DC应用电路

LT3980的RT脚对地接一个97.6K的电阻,设定LT3980的工作频率为固定的400KHz,RT电阻为32.4K时的工作频率则为1MHz.在这种使用外部电阻设置开关频率的DC/DC变换器中,可以加一个稳压管Z1和限流电阻R1用以在输入电压增加时降低开关频率。

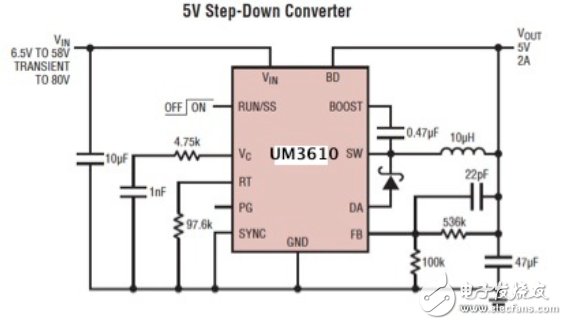

图2: 通过外接电阻和稳压管调整DC/DC稳压器的典型电路

在高输入电压下,由于频率降低,而电感值又一定,所以输出的电流和电压纹波增加。频率在较宽的范围内变化时,电感无法优化地工作,环路的补偿也无法优化。这样我们就需要在图2的电路中增加R2和Z2来限制频率的变化范围。外接电阻的方法需要系统工程师作仔细的计算,而且容易受到寄生参数的影响。这里我们通过内部电路检测输入电压的变化自动调整开关频率,简化应用电路设计。

(一)电流控制模式的DC/DC降压变压器

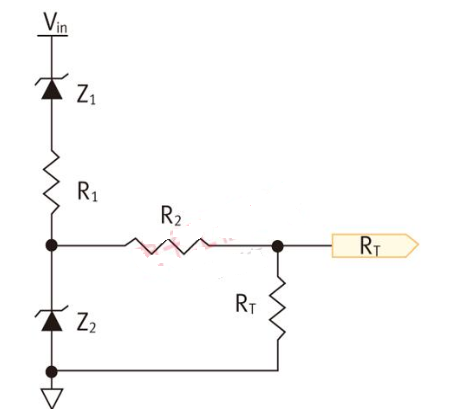

图3是电压控制模式的DC/DC转换器系统结构。其中,EA为误差放大器,PWM为PWM比较器,Soft start为软启动模块,Band gap reference为带隙基准源,OSP为降频保护电路,Oscillator为振荡器,Logic Latch为逻辑触发器,Driver为驱动开关管PMOS的驱动电路,OCP为过流保护,UVLO为欠压保护,OTP为过热保护。

图3: 电压控制模式的DC/DC降压变换器原理框图

电路采用具有降频功能的电压型PWM控制模式,输出电压误差小。在图中,PWM控制部分是由误差放大器和PWM比较器组成,反馈电压和基准电压比较后,放大差值以产生一个误差信号,并经过一定的零级点补偿后,提供到PWM比较器的一端输入,同时比较器的另一端输入是振荡器电路提供的一定频率的脉冲时钟信号。

这个信号将被传输到后端的逻辑电路部分,该部分包括RS触发器,以及包含多种保护信号的相关逻辑,它通过接通和断开驱动电路来控制电源开关的状态,从而设置变换器的工作频率,设定功率管的占空比。图中OSP比较器,主要作用是,当输出电压过低,效率下降时,经过OSP信号控制振荡器,以降低PWM比较器输入端的时钟信号,从而在相同情况下提高变换器的转换效率。

电路中采用双电源,Vdd由输入电压Vcc通过一个高压线性稳压器转换而成,为3.3V,而Vcc为输入高电压,用于供给使能迟滞电路、带隙基准源、Vdd生成电路、过流保护以及驱动电路,这些电路中的MOS管,采用高压DMOS器件,防止击穿;而其他与输入电压无关的电路,则有Vdd供给,其中的MOS管,采用CMOS器件。

目前峰值电流控制模式DC/DC转换器的应用更广泛,它的原理框图如图4所示。

图4: 峰值电流控制模式的DC/DC降压变换器原理框图

对应于电压控制模式,电流控制模式的DC/DC转换器以几乎无穷大的开环环路增益来调节DC/DC的输出电流,其实是一个高输出阻抗的电流源。如图4所示,在电流控制模式的DC/DC降压变换器中,快速高增益的电流环路和慢速的电压控制回路嵌套使用,电感电流与斜坡补偿后的锯齿波合成的信号和电压误差信号相比较产生控制信号,当输出电压跌落时,控制功率管打开向负载提供更多的电流来保持输出电压的稳定。电流控制模式的DC/DC测量电感电流,将输出变为恒流源输出,使DC/DC的输出级由电压模式的双极点系统转变为单极点系统,从而更容易进行补偿,提高稳定性。

(二)振荡器的设计

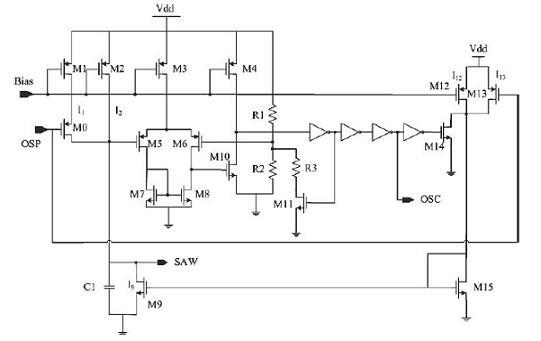

振荡器电路在DC/DC集成电路中有广泛的用途。振荡时钟为内部电路提供开关脉冲的同步,且衍生出锯齿波,提供给PWM比较器。是电压模式和电流模式DC/DC转换器的基本单元。图5为本文设计的振荡电路,设计中采用恒流充放电结构,充电电流为I1+I2(降频时为I1),放电电流为I12+I13(降频时为I12)。

图5: 振荡频率受控制的振荡电路

从图5中可知,M1、M2为电容充电,M9为电容放电,这些决定了振荡器的时钟频率。

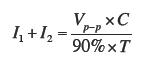

首先,假设输出振荡电压与充放电电流成正比。基于这个假设,偏置电流就可以确定。如果希望频率为800K(T=1.25us),上升时间为总周期的90%(1.125us),而要求输出锯齿波SAW的峰峰值Vp-p为1V.那么,充电电流为

公式3

其中C为C1的电容值,T为振荡周期。

从电路图可以看出,振荡波形的转折点可以由下式决定:

公式4

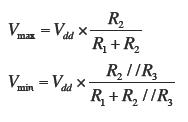

图6为振荡器的输出波形,从图中可以看出,振荡波形在0.6V至1.8V范围内波动,符合设计要求。

图6: 振荡器的输出波形

当输出输入电压比值低于一定值(0.2)时,说明此时控制脉冲的占空比很低,效率下降,此时通过低比值保护电路,产生OSP信号,将整体电路的频率下降。从电路图可以看出,当OSP通过控制电路变为高电平时,则M0关闭,而M1与M2的宽长比为4:1,此时的充电电流变为原来的1/4,那么充电时间变为原来的4倍,这样输出振荡波的频率变为原来的1/4,即200KHz,提高电源的转换。

(三)应用

在汽车电子应用中,输入电压有12V,24V和36V等多种电压轨,在确定输出电压的条件下,这种可以根据输入电压自适应调整工作频率的DC/DC可以自动设置合适的工作频率,优化DC/DC的工作效率,减小瞬态过程。